|

Все про Assembler українською мовою на сайті net.kr.ua |

|

|

|

|

|||

|

|

|||||

|

|

|

|

|

Додаткові режими адресації

Режими адресації

32-розрядних процесорів розроблені, виходячи з вимог утворення 32-бітового

зсуву. Іншими словами, вони призначені для 32-розрядних застосувань, в яких

сегменти даних або стека (як, втім, і сегменти команд) можуть мати розміри 232

= 4 Гбайт. Проте в реальному режимі розмір будь-якого сегменту обмежується величиною

216 = 64 Кбайт, і 32-бітові зсуви не

мають сенсу. З іншого боку, ніщо не заважає нам використовувати для

утворення 16-бітового зсуву 32-розрядні регістри (ЕВХ, ESI і інш.), якщо, звичайно,

їх реальний вміст не перевищуватиме величини Ffffh. Вказівка як операнди

команд 32-розрядних регістрів дозволяє використовувати додаткові можливості

32-розрядних процесорів по частині адресації пам'яті, що в деяких випадках

може виявитися корисним. Слід підкреслити, що мова йде тут тільки про

ті операнди, або, правильніше сказати, аргументах команди, які описують

непряму (через регістри) адресацію пам'яті.

На відміну від МП 86, де базовими регістрами можуть бути тільки ВХ і ВР, а індексними

тільки SI і DI, 32-розрядні процесори допускають використання в якості і

базових, і індексних практично всіх регістрів загального призначення. Таким чином,

цілком законна команда вигляду

mov ЕАХ[ЕСХ][EDX]

Друга відмінність полягає в можливості масштабування вмісту індексного регістра, тобто множення його на заданий в команді коефіцієнт, який може набувати значень 1, 2, 4 або 8. Приклад такої адресації:

inc word ptr [ЕАХ] [Есх*2]

Ще раз підкреслимо, що додаткові режими непрямої адресації вимагають використання 32-розрядних регістрів. Команди

inc word ptr [AX] [Ecx*2]

або

inc word ptr [ЕАХ] [Сх*2]

розглядаються асемблером,

як неправильні.

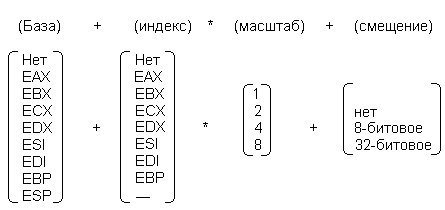

Режими

непрямої адресації пам'яті, що надаються 32-розрядними процесорами

при використанні 32-розрядних регістрів, зображені на мал. 4.2.

З малюнка видно, що як базовий можна використовувати всі

регістри загального призначення, включаючи навіть

покажчик стека ESP. При цьому, якщо як

базовий виступає один з регістрів ESP або ЕВР, то за умовчанням адресація

здійснюється через сегментний регістр SS, хоча можлива заміна сегменту. У решті

всіх випадків адресація за умовчанням здійснюється через сегментний

регістр DS.

Використання регістра ЕВР як індексний не адресує нас до стека: адресація попрежнему

здійснюється за допомогою регістра DS.

Мал. 4.2. Режими непрямої

адресації з використанням 32-розрядних регістрів.

Прочерк в другій колонці підкреслює, що регістр ESP не можна використовувати як індексного. Це не означає, що ESP не можна указувати як другий операнд:

mov ЕАХ[ЕСХ][ESP]

Недопустима тільки конструкція,

в якій вміст ESP умножається на масштабуючий множник:

mov ЕАХ[ЕСХ][Esp*8]

Корисно також відзначити, що зсув в команді

вигляду

mov ЕАХ[ЕВХ][ЕСХ]+20

може бути тільки або 8-бітовим,

або 32-бітовим. 16-бітові зсуви не утворюються. Якщо вказана в команді

величина зсуву поміщається в байт, як це має місце в приведеному вище

прикладі команди, то зсув в коді команди займає 1 байт. Якщо ж величина

зсуву більше 255, то під нього в коді команди відводиться відразу 32 битий.

Таким чином, поняття базової і індексної адресації в 32-розрядних процесорах

декілька розмиваються. Якщо регістр указується з масштабуючим множником,

то це, звичайно, індексна адресація. Якщо ж множник відсутній, то адресацію

і через ЕВХ, і через ESI з рівним успіхом можна віднести як до базової, так і

до індексної.

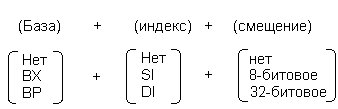

Використання для адресації пам'яті 16-розрядних регістрів різко звужує можливості

адресації 32-розрядних процесорів (мал. 4.3). В цьому випадку ми фактично маємо

справу з МП 86.

Мал. 4.3. Режими непрямої

адресації з використанням 16-розрядних регістрів.

Нагадаємо, що в 16-розрядному режимі допустимі не всі поєднання базових і індексних регістрів. Як базовий регістр можна використовувати тільки ВХ або ВР, а як індексний тільки SI або DI.

|

|

|

|

|

||||

|

|

|

|||

|

|

|||

|

|

|

Copyright © net.kr.ua, 2019-2026 (assem.us) |