|

Все про Assembler українською мовою на сайті net.kr.ua |

|

|

|

|

|||

|

|

|||||

|

|

|

|

Архітектурні особливості

Операційна система MS-DOS, мова асемблера МП

86 і методи програмування мікропроцесорів корпорації Intel

розроблялися стосовно 16-розрядного процесора 8086 і тому режиму, який згодом

отримав назву реальну. Поява процесора 80386 знаменувало собою почато нового

етапу в розвитку операційних систем і прикладного програмування -

етапу багатозадачних графічних операційних систем захищеного режиму типу Windows

і 32-розрядних прикладних програм. При цьому, як вже наголошувалося у введенні,

всі архітектурні засоби 86-го процесора входять до складу будь-якого сучасного

процесора, який, таким чином, можна умовно розділити на дві частини - МП 86

і додаткові засоби, що забезпечують захищений режим, 32-розрядну адресацію і

інше. З цих додаткових засобів можна виділити ті, які забезпечують захищений

режим, і в реальному режимі не використовуються (в усякому разі,

явним чином; насправді, процесор, навіть працюючи в реальному режимі, використовує принаймні

деякі з цих засобів). Сюди, наприклад, відносяться регістри таблиць дескрипторів,

регістри тестування і відладки, привілейовані команди захищеного режиму,

система сторінкового відображення адрес і ін. З іншого боку, частину нових

властивостей сучасних процесорів можна використовувати і в реальному режимі, виконуючи

програми під управлінням MS-DOS. Сюди, перш за все, відноситься

використання 32-бітових операндів, деяких нових команд процесора і розширених

можливостей старих команд. Справжній розділ буде в основному присвячений саме цим

засобам процесорів 80386, i486 і Pentium, які надалі ми узагальнено називатимемо 32-розрядними

процесорами. Питання про програмування захищеного режиму дуже складне, щоб

його можна було освітити в рамках цієї книги, хоча основні принципи захищеного

режиму будуть описані.

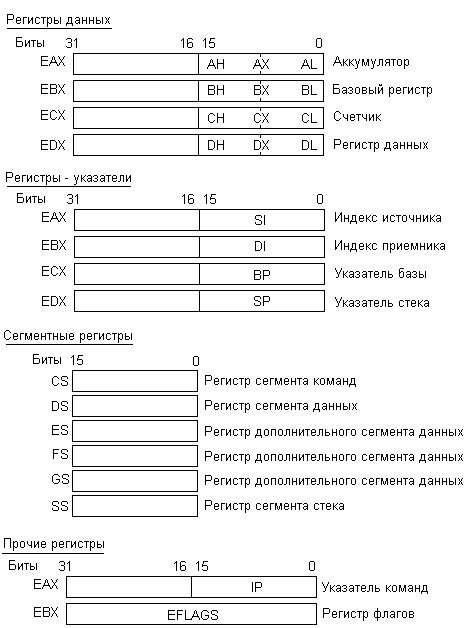

32-розрядні процесори

містять декілька десятків программно- регістрів (не

рахуючи регістрів

співпроцесора), що адресуються, з яких шість є 16-розрядними, а

останні - 32-розрядними. Регістри прийнято об'єднувати в сім груп: регістри загального

призначення (або регістри даних), регістри-покажчики, сегментні регістри, регістри,

що управляють, регістри системних адрес, налагоджувальні регістри і регістри

тестування. Крім того, в окрему групу виділяють лічильник команд і регістр

прапорів. Регістри, використовувані в реальному режимі, показані на мал. 4.1.

Мал. 4.1. Основні регістри 32-розрядних процесорів.

Як видно з мал. 4.1,

регістри загального призначення і регістри-покажчики відрізняються від аналогічних регістрів

МП 86 тим, що вони є 32-розрядними. Відповідно, до їх мнемонічних

позначень додана буква Е (від extended, розширений).

Для збереження сумісності з ранніми моделями процесорів допускається звернення

до молодших половин всіх регістрів, які мають ті ж мнемонічні позначення,

що і в МП 86 (АХ, Вх,сх, DX, SI, DI, ВР і SP). Природно, збережена можливість

роботи з молодшими (AL, BL, CL і DL) і старшими (АН, ВН, СН і

DH) половинками

регістрів МП 86. Проте старші половини 32-розрядних регістрів не мають мнемонічних

позначень і безпосередньо недоступні. Для того, щоб прочитати, наприклад,

вміст старшої половини регістра ЕАХ (биті 31...16) доведеться зрушити весь

вміст ЕАХ на 16 битий управо (у регістр АХ) і прочитати потім вміст

АХ. Всі регістри загального призначення і покажчики програміст може використовувати

на свій розсуд для тимчасового зберігання адрес і даних розміром від байта

до подвійного слова. Так, наприклад, можливе використання наступних команд:

mov Еах,0ffffffffh ;Работа з подвійним словом (32 битий)

mov Ax,0ffffh ;Работа із словом (16 битий)

mov AL, 0ffh ;Работа з байтом (8 битий)

Всі сегментні регістри,

як і в МП 86, є 16-розрядними. У їх склад включено ще два регістри

- FS і GS, які можуть використовуватися для зберігання сегментних адрес двох

додаткових сегментів даних. Таким чином, при використанні розширених

можливостей сучасних процесорів програмі одночасно доступні чотири

сегменти даних, а не два, як в МП 86.

Регістр покажчика команд також є 32-розрядним і зазвичай при описі процесора

його називають EIP. Молодші шістнадцять розрядів цього регістра відповідають

регістру IP процесора МП 86. Весь регістр EIP використовується тільки в 32-розрядних

застосуваннях; у 16-розрядних програмах адреси можуть бути тільки 16-розрядними

і, відповідно, для адресації в програмному сегменті використовується молодша

половина регістра EIP.

Регістр прапорів прийнято називати EFLAGS (від extended

flags, розширені прапори).

Хоча він має довжину 32 битий, тільки молодші 18 біт (да і то не все) містять

значущу інформацію. Додатково до шести прапорів стану

(CF, PF, AF, ZF,

SF і OF) і трем прапорам управління станом процесора

(TF, IF і DF), призначення

яких було описане в гл. 1, він включає нові прапори завдання, рестарту і віртуального

режиму, а також двобайтове поле привілеїв введення-виводу. Всі ці біти використовуються

тільки в захищеному режимі і тут розглядатися не будуть.

|

|

|

|

||||

|

|

|

|||

|

|

|||

|

|

|

Copyright © net.kr.ua, 2019-2026 (assem.us) |